Media Oriented Systems Transport

**Multimedia and Control Networking Technology**

OS8104

MOST Network Transceiver

Final Product Data Sheet

DS8104FP4

Jan. 2003

## **Ordering Information**

#### Valid Part Numbers:

| Order Number | Grade         |                            | Pookogo                    |

|--------------|---------------|----------------------------|----------------------------|

| Order Number | Temperature   | Femperature Supply Package |                            |

| OS8104AQ     | -40 to +85° C | 4.5 to 5.5 V               | 44-pin TQFP                |

| OS8104AQR    | -40 to +85° C | 4.5 to 5.5 V               | 44-pin TQFP, Tape and Reel |

This table represents parts that were available at the time of printing and may not represent parts that are currently available. For the latest list of valid ordering numbers for this product, please contact your local sales office.

## **Support and Further Information**

For more information on Oasis SiliconSystems products, including integrated circuits, software, and MOST development tools and modules, contact one of our offices below, or visit our web site:

www.oasis.com

Oasis SiliconSystems, Inc.

1120 Capital of Texas Hwy South Building 2, Suite 100 Austin, Texas 78746 USA

Tel: (+1) 512 306-8450 Fax: (+1) 512 306-8442 OSS@oasis.com

Oasis SiliconSystems, Inc.

38600 Van Dyke Avenue

Suite 220

Sterling Heights, Michigan 48312 USA

Tel: (+1) 586 795-0545 Fax: (+1) 586 795-8950 Detroit@oasis.com Oasis SiliconSystems AG

Bannwaldallee 48 D-76185 Karlsruhe Germany

Tel: (+49) (0) 721 6 25 37 - 0 Fax: (+49) (0) 721 6 25 37 - 119 OSS@oasis.de

Oasis SiliconSystems AG Japan

Shin-Yokohama UU Bldg. 5F 2-5-2 Shin-Yokohama, Kohoku-ku Yokohama 222-0033, Japan

Tel: (+81) 45-470 2240 Fax: (+81) 45-470 2242 Japan@oasis.com

## **Technical Support**

For technical support please refer to one of the following e-mail addresses:

support@oasis.de support@oasis.com

## **Intellectual Property**

© Copyright 1997-2003 Oasis SiliconSystems. All rights reserved. Duplication of this document without permission is prohibited.

### **Trademarks**

MOST is a registered trademark of Oasis SiliconSystems. All other trademarks used in this document are the property of their respective owners.

#### **Patents**

There are a number of patents and patents pending on the MOST technology. The rights to these patents are not granted without any specific Agreement between the users and the patent owners.

## **Conventions**

Within this manual, the following abbreviations and symbols are used to improve readability.

| Example         | Description                                                                                                                                                 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT             | Name of a single bit within a register                                                                                                                      |

| REG.BIT         | Name of a single bit (BIT) in register REG                                                                                                                  |

| xy              | Range from x to y, inclusive                                                                                                                                |

| BITS[m:n]       | Groups of bits (or pins) from m to n, inclusive                                                                                                             |

| PIN             | Pin Name                                                                                                                                                    |

| 0xzzz           | Hexadecimal number (value zzz)                                                                                                                              |

| zzh             | Hexadecimal number (value zz)                                                                                                                               |

| rsvd            | Reserved memory location. Must write 0, read value indeterminate                                                                                            |

| code            | Instruciton code                                                                                                                                            |

| Multi Word Name | Used for multiple words that are considered a single unit, such as: Resource Allocate message, or Connection Label, or Decrement Stack Pointer instruction. |

| Section Name    | Section or Document name.                                                                                                                                   |

| VAL             | Over-bar indicates active low pin or register bit                                                                                                           |

| bREG            | Single byte MOST register                                                                                                                                   |

| mBUF            | Multi-byte MOST buffer                                                                                                                                      |

| Х               | Don't care                                                                                                                                                  |

## **Revision History**

| Revision | Date       | Description                          |

|----------|------------|--------------------------------------|

| 1.1      |            | Initial OS8104 Data Sheet            |

| PP2      | Sept. 2000 | Fully revised.                       |

| FP1      | Dec. 2000  | Final Product Data Sheet             |

| FP2      | Dec. 2000  | Final Product Data Sheet, revision 2 |

| FP3      | Jan. 2003  | Final Product Data Sheet, revision 3 |

| FP4      | Jan. 2003  | Final Product Data Sheet, revision 4 |

## **TABLE OF CONTENTS**

| LIST OF FIGURES                                                                      | 10 |

|--------------------------------------------------------------------------------------|----|

| LIST OF TABLES                                                                       | 12 |

| 1 INTRODUCTION                                                                       | 15 |

| 2 FUNCTIONAL DESCRIPTION                                                             | 17 |

| 2.1 Network Interface & Compatibility                                                | 17 |

| 2.2 On-Chip Network Management                                                       |    |

| 2.2.1 Channel Allocation                                                             | 19 |

| 2.2.2 Physical Position Sensing                                                      | 19 |

| 2.2.3 Network Delay Detection                                                        |    |

| 2.2.4 Node Alive Supervision                                                         |    |

| 2.3 On-Chip Power Management                                                         |    |

| 2.4 Data Transfer Methods                                                            |    |

| 2.5 Bandwidth                                                                        |    |

| 2.5.1 Control Messaging                                                              |    |

| 2.5.2 Synchronous (Stream) Data                                                      |    |

| 2.5.3 Asynchronous (Packet) Data                                                     |    |

|                                                                                      |    |

| 3 MAIN FUNCTIONAL BLOCKS                                                             |    |

| 4 CONFIGURATION                                                                      | 27 |

| 5 CONTROL PORT IN SERIAL MODE                                                        | 29 |

| 5.1 I <sup>2</sup> C Mode                                                            | 30 |

| 5.1.1 Writing to the Control Port                                                    |    |

| 5.1.2 Reading from the Control Port                                                  |    |

| 5.2 SPI Mode                                                                         |    |

| 5.2.1 Writing to the Control Port                                                    |    |

| 5.2.2 Reading from the Control Port                                                  | 32 |

| 6 NETWORK INTERFACE                                                                  | 35 |

| 6.1 MOST Frame Structure                                                             | 35 |

| 6.2 Network Configuration                                                            | 36 |

| 6.2.1 bXCR (Transceiver Control Register)                                            |    |

| 6.2.2 bXSR (Transceiver Status Register)                                             |    |

| 6.2.3 bXSR2 (Transceiver Status Register 2)                                          |    |

| 6.2.4 Transceiver Error Events                                                       |    |

| 6.2.5 bSBC (Synchronous Bandwidth Control Register) 6.2.6 bNDR (Node Delay Register) |    |

| 6.2.7 bNPR (Node Position Register)                                                  |    |

| 6.2.8 bMPR (Maximum Position Register)                                               |    |

| 6.2.9 bMDR (Maximum Delay Register)                                                  |    |

| 6.2.10 Network Registers After Lock                                                  |    |

| 7 SOURCE PORTS IN SERIAL MODE                                                        | 43 |

| 7.1 Serial Source Port Interface                                                     | 44 |

| 7.2 Source Port Configuration (Serial)                                               |    |

| 7.2.1 bSDC1 (Source Data Control Register 1)                                         |    |

|                                                                                      |    |

|   | 7.2.1.1 I <sup>2</sup> S (Philips) Source Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47                                                                               |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|   | 7.2.1.2 Sony Source Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

|   | 7.2.1.3 Matsushita Source Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48                                                                               |

|   | 7.2.2 bSDC2 (Source Data Control Register 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48                                                                               |

|   | 7.2.3 bSDC3 (Source Data Control Register 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

|   | 7.3 Serial Source Port Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50                                                                               |

|   | 7.3.1 Source Port Mode 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                               |

|   | 7.3.2 Source Port Mode 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                               |

|   | 7.3.3 Source Port Mode 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   | 7.3.4 Source Port Mode 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   | 7.3.5 Source Port Mode 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   | 7.3.6 Source Port Mode 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   | 7.3.7 Source Port Mode 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   | 7.3.8 Source Port Mode 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   | 7.3.9 Source Port Mode 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   | 7.3.10 Source Port Mode 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

|   | 7.3.11 Source Port Mode 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

|   | 7.4 S/PDIF (IEC-60958)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|   | 7.4.1 Synchronizing To S/PDIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

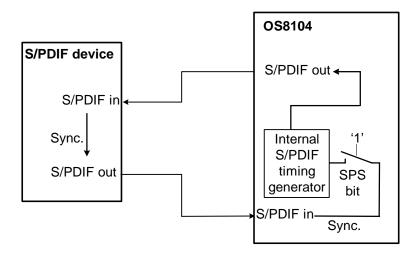

|   | 7.4.2 Routing S/PDIF Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   | 7.4.3 S/PDIF Speed Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   | 7.4.4 S/PDIF Data To S/PDIF Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|   | 7.4.5 S/PDIF Data To Non-S/PDIF Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

|   | 7.4.6 Non-S/PDIF Data To S/PDIF Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

|   | 7.5 Transparent Data Transport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60                                                                               |

| 8 | PARALLEL ACCESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                                                                               |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

|   | 8.1 Control Port in Parallel Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62                                                                               |

|   | 8.1 Control Port in Parallel Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

|   | 8.1.1 Writing to the Control Port MAP Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63                                                                               |

|   | 8.1.1 Writing to the Control Port MAP Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63                                                                               |

|   | 8.1.1 Writing to the Control Port MAP Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63<br>63                                                                         |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63<br>62<br>65                                                                   |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63<br>64<br>65                                                                   |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63<br>64<br>65<br>66                                                             |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63<br>64<br>65<br>66                                                             |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 63<br>64<br>65<br>66<br>66                                                       |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63<br>65<br>66<br>66<br>68                                                       |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>64<br>65<br>66<br>66<br>68                                                 |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63<br>63<br>64<br>65<br>66<br>66<br>66<br>68<br>68                               |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>                                                                           |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.4 Writing 8 Bytes into the FIFO                                                                                                                                                                                                                                                                                                                                                                                                     | 63<br>64<br>66<br>66<br>68<br>68<br>68<br>69                                     |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP                                                                                                                                                                                                                                                                                                                                                                                                                                           | 636364656668686970                                                               |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.4 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 1 Byte into the FIFO                                                                                                                                                                                                                                                                                                                                                                | 6363646566666868697071                                                           |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.4 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 1 Byte into the FIFO 8.2.2.6 Reading 8 Bytes from the FIFO                                                                                                                                                                                                                                                                                                                          | 63<br>64<br>65<br>66<br>66<br>67<br>68<br>68<br>69<br>70<br>71                   |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.4 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 1 Byte into the FIFO 8.2.2.6 Reading 8 Bytes from the FIFO 8.2.3 (bSP) Source Port Status Register                                                                                                                                                                                                                                                                                  | 63<br>64<br>65<br>66<br>66<br>67<br>68<br>68<br>69<br>70<br>71<br>71             |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.3 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 1 Byte into the FIFO 8.2.2.6 Reading 8 Bytes from the FIFO 8.2.3 (bSP) Source Port Status Register 8.3 Parallel-Combined/Physical Mode                                                                                                                                                                                                                                              | 63<br>63<br>64<br>65<br>66<br>66<br>67<br>68<br>68<br>69<br>70<br>71<br>71<br>72 |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.4 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 1 Byte into the FIFO 8.2.2.6 Reading 8 Bytes from the FIFO 8.2.3 (bSP) Source Port Status Register 8.3 Parallel-Combined/Physical Mode 8.3.1 Configuring Parallel-Combined (Physical) Mode 8.3.2 Asynchronous Data Packets 8.3.3 Receiving Source Data                                                                                                                              | 63636465666868697071727275                                                       |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.4 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 1 Byte into the FIFO 8.2.2.6 Reading 8 Bytes from the FIFO 8.2.3 (bSP) Source Port Status Register 8.3 Parallel-Combined/Physical Mode 8.3.1 Configuring Parallel-Combined (Physical) Mode 8.3.2 Asynchronous Data Packets 8.3.3 Receiving Source Data 8.3.3.1 Received Asynchronous Status Bytes                                                                                   | 63636465666868697171727275                                                       |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing into the FIFO 8.2.2.4 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 1 Byte into the FIFO 8.2.2.6 Reading 8 Bytes from the FIFO 8.2.3 (bSP) Source Port Status Register 8.3 Parallel-Combined/Physical Mode 8.3.1 Configuring Parallel-Combined (Physical) Mode 8.3.2 Asynchronous Data Packets 8.3.3 Receiving Source Data 8.3.3.1 Received Asynchronous Status Bytes 8.3.3.2 Moving Received Asynchronous Status Bytes                           | 6363646566686869717172737575                                                     |

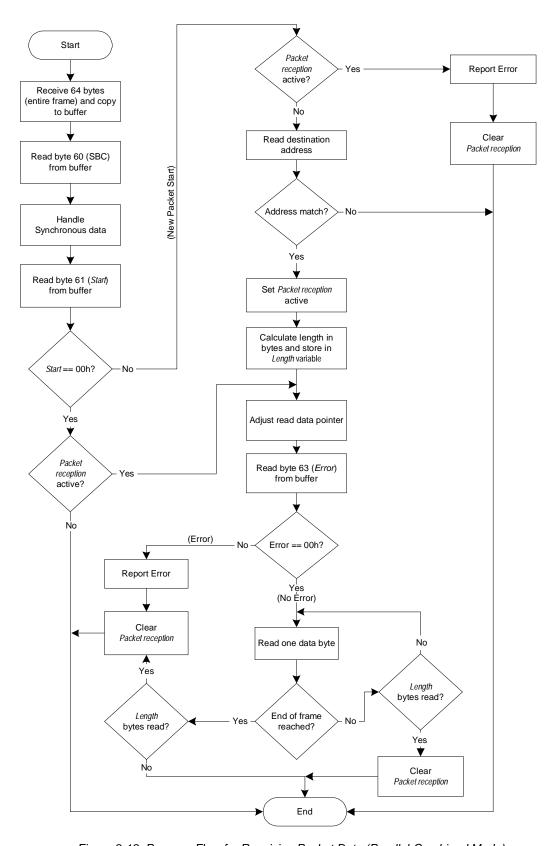

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.3 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 8 Bytes into the FIFO 8.2.2.6 Reading 8 Bytes from the FIFO 8.2.3 (bSP) Source Port Status Register 8.3 Parallel-Combined/Physical Mode 8.3.1 Configuring Parallel-Combined (Physical) Mode 8.3.2 Asynchronous Data Packets 8.3.3 Receiving Source Data 8.3.3.1 Received Asynchronous Status Bytes 8.3.3.2 Moving Received Asynchronous Status Bytes 8.3.3.3 Handling Received Data | 636364656666686971727273747577                                                   |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.3 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 1 Byte into the FIFO 8.2.2.6 Reading 8 Bytes from the FIFO 8.2.3 (bSP) Source Port Status Register 8.3 Parallel-Combined/Physical Mode 8.3.1 Configuring Parallel-Combined (Physical) Mode 8.3.2 Asynchronous Data Packets 8.3.3 Received Asynchronous Status Bytes 8.3.3.1 Received Asynchronous Status Bytes 8.3.3.2 Moving Received Data 8.3.4 Transmitting Data                 | 63636465666668697171727374757575                                                 |

|   | 8.1.1 Writing to the Control Port MAP Data Register 8.1.2 Writing to the Control Port 8.1.3 Reading from the Control Port 8.1.4 bCP (Control Port Status Register) 8.2 Source Ports in Parallel Mode 8.2.1 Parallel-Synchronous Mode 8.2.1.1 Reading from the FIFO 8.2.1.2 Writing into the FIFO 8.2.2 Parallel-Asynchronous Mode 8.2.2.1 Memory Address Pointer (MAP) 8.2.2.2 Writing into the FIFO 8.2.2.3 Writing the MAP 8.2.2.3 Writing 8 Bytes into the FIFO 8.2.2.5 Writing 8 Bytes into the FIFO 8.2.2.6 Reading 8 Bytes from the FIFO 8.2.3 (bSP) Source Port Status Register 8.3 Parallel-Combined/Physical Mode 8.3.1 Configuring Parallel-Combined (Physical) Mode 8.3.2 Asynchronous Data Packets 8.3.3 Receiving Source Data 8.3.3.1 Received Asynchronous Status Bytes 8.3.3.2 Moving Received Asynchronous Status Bytes 8.3.3.3 Handling Received Data | 63636465666668697171727374757575                                                 |

| 0.2.4.2 Dranging Booket Date                        | ,   |

|-----------------------------------------------------|-----|

| 8.3.4.2 Preparing Packet Data                       | ۵۵  |

| 8.3.4.4 Priority                                    |     |

| 8.3.4.5 Idle SF Intervals                           |     |

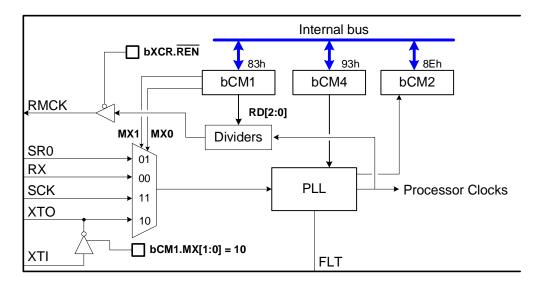

| 9 CLOCK MANAGER                                     |     |

| 9.1 Clock Manager Registers                         |     |

| 9.2 PLL Lock Status                                 |     |

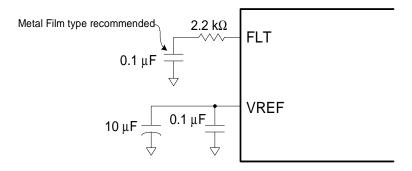

| 9.3 VREF and FLT Pins                               |     |

|                                                     |     |

| 9.4 Crystal Pins (XTI/XTO)                          |     |

| 10 POWER MANAGEMENT                                 | 93  |

| 10.1 Low-Power Mode                                 |     |

| 10.1.1 Entering Low-Power Mode                      |     |

| 10.1.2 Leaving Low-Power Mode                       |     |

| 10.2 Zero-Power Mode                                |     |

| 10.2.1 Entering Zero-Power Mode                     |     |

| 10.2.2 WAKE_UP and R_TIMER Pins                     |     |

| 10.2.3 Leaving Zero-Power Mode                      | 94  |

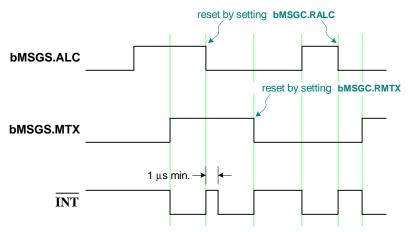

| 11 INTERRUPT HANDLING                               | 95  |

| 11.1 bIE (Interrupt Enable Register)                | 95  |

| 11.2 Power-On Interrupt                             |     |

| 11.3 Behavior on Multiple Interrupts                |     |

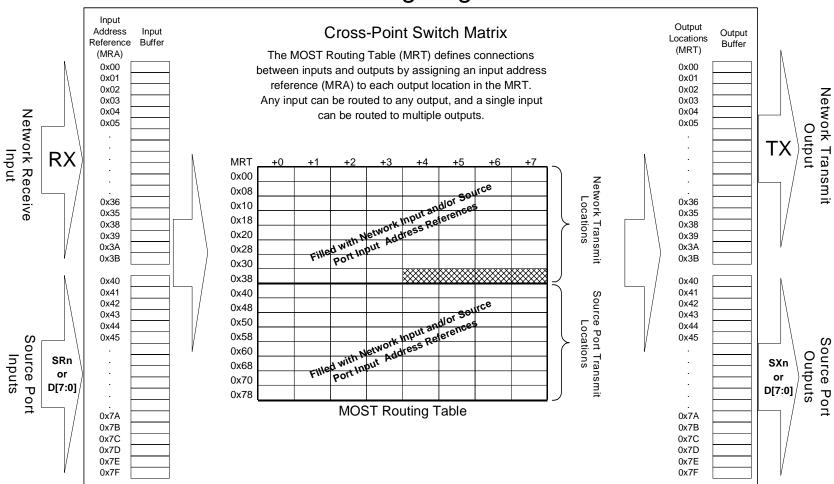

| 12 MOST ROUTING TABLE                               |     |

|                                                     |     |

| 12.1 Incoming Network Data to Outgoing Network Data |     |

| 12.2 Serial Source Port Inputs to Network           |     |

| 12.3 Network to Serial Source Port Outputs          |     |

| 12.4 Synchronous Parallel Port Data Transfers       |     |

| 12.4.1 Synchronous Parallel Data To Network         |     |

| 12.4.2 Network to Synchronous Parallel Data         |     |

| 12.5 Transparent Channel Data Routing               |     |

| 12.6 Address Reference 0xF8                         |     |

| 12.7 MRT Power-up Defaults                          |     |

| 12.8 Routing Limitations                            | 110 |

| 13 CONTROL MESSAGES                                 | 111 |

| 13.1 Transmit Message Addressing                    | 112 |

| 13.1.1 Node Address (Logical Addressing)            | 112 |

| 13.1.2 Node Position Address (Physical Addressing)  |     |

| 13.1.3 Group Address/Groupcast                      |     |

| 13.1.4 Special Broadcast Address                    |     |

| 13.1.5 Address Ranges vs. Addressing Modes          |     |

| 13.1.6 bNAH, bNAL (Node Address Registers)          |     |

| 13.1.7 bGA (Group Address Register)                 |     |

| 13.2 Managing Control Messages                      |     |

| 13.2.1 bMSGC (Message Control Register)             |     |

| 13.2.2 bMSGS (Message Status Register)              |     |

| 13.2.3 bXTS (Transmit Status Register)              |     |

| 13.2.4 bXRTY (Transmit Retry Register)              |     |

| 13.2.5 bXTIM (Transmit Retry Time Register)         | 118 |

|                                                       | ,   |

|-------------------------------------------------------|-----|

| 13.2.6 mRCMB (Receive Control Message Buffer)         |     |

| 13.2.7 mXCMB (Transmit Control Message Buffer)        |     |

| 13.3 Control Message Reception                        |     |

| 13.4 Control Message Transmission                     |     |

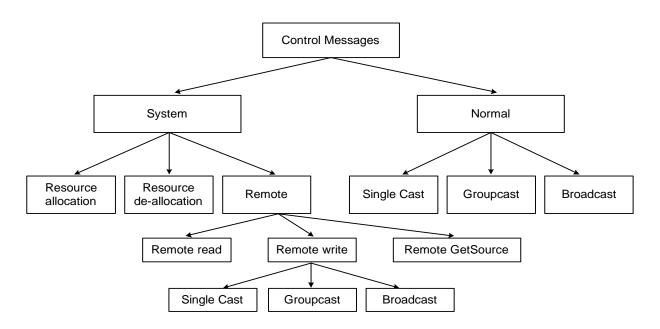

| 13.5 Control Message Types                            |     |

| 13.5.1 Received Control Message Types                 |     |

| 13.5.2 Transmit Control Message Types                 |     |

| 13.5.2.1 Normal Messages (Type 00h)                   |     |

| 13.5.2.3 Remote Write Message (Type 011)              |     |

| 13.5.2.4 Resource Allocate Message (Type 03h)         |     |

| 13.5.2.5 Resource De-Allocate Message (Type 04h)      |     |

| 13.5.2.6 Remote GetSource Message (Type 05h)          |     |

| RESOURCE ADMINISTRATION                               | 131 |

| 14.1 mCRA (Channel Resource Allocation Table)         | 131 |

| 14.1.1 mCRA in Timing-Slave Nodes                     |     |

| 14.1.2 mCRA in the Timing-Master Node                 |     |

| 14.2 Allocating Network Resources                     |     |

| 14.3 De-Allocating Network Resources                  |     |

| PACKET DATA TRANSFER                                  | 135 |

| 15.1 Packet Transfer Registers                        | 135 |

| 15.1.1 bAPAH (Alternate Packet Address High Register) |     |

| 15.1.2 bAPAL (Alternate Packet Address Low Register)  |     |

| 15.1.3 bPLDT (Packet Transmit Length Register)        |     |

| 15.1.4 bPPI (Packet Priority Register)                |     |

| 15.1.5 bPCTC (Packet Control Register)                |     |

| 15.1.6 bPSTX (Packet Start Tx Register)               |     |

| 15.1.7 bPCTS (Packet Status Register)                 |     |

| 15.1.8 mARP (Asynchronous Receive Packet Buffer)      |     |

| 15.1.9 mAXP (Asynchronous Transmit Packet Buffer)     |     |

| 15.2 Asynchronous Interrupt Pin (AINT)                |     |

| 15.3 Packet Data Handling                             |     |

| 15.3.1 Preparing Packet Data for Transmission         |     |

| 15.3.2 Polling-Based Packet Data Handling             |     |

| 15.3.3 Interrupt-Based Packet Data Handling           |     |

| OS8104 STARTUP                                        | 143 |

| 16.1 Set Up After Power Up Reset                      | 144 |

| 16.2 Timing-Master Mode                               | 145 |

| 16.3 Timing-Slave Mode                                | 146 |

| 16.4 Version Number                                   | 146 |

| STAND-ALONE MODE                                      | 147 |

| 17.1 Entering Stand-Alone mode                        | 147 |

| 17.2 Registers                                        | 147 |

| 17.3 mSIMB (Stand-Alone Control Port Message Buffer)  | 148 |

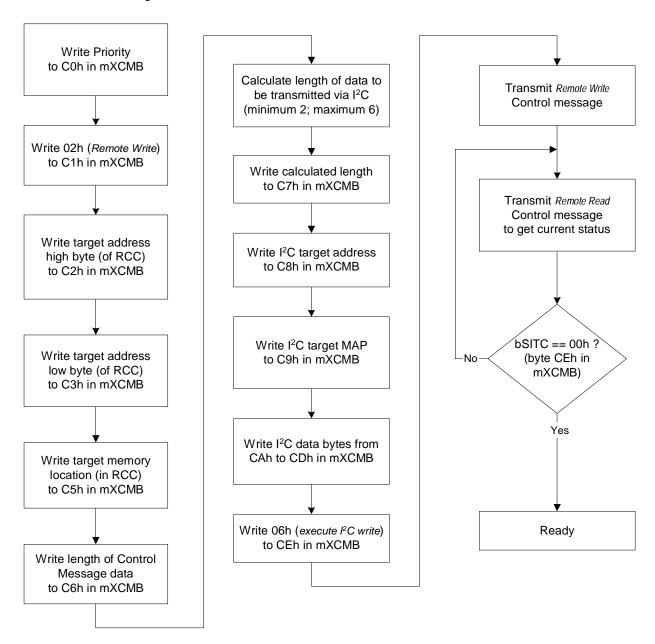

| 17.4 Writing to External Peripherals                  | 149 |

| 17.5 Reading from External Peripherals                | 152 |

| 17.6 Message on Interrupt                             | 153 |

|                                                       |     |

| 18 ELECTRICAL CHARACTERISTICS                       | 155 |

|-----------------------------------------------------|-----|

| 18.1 Absolute Maximum Ratings                       |     |

| 18.3 Thermal Characteristics                        | 155 |

| 18.4 DC Characteristics                             | 156 |

| 18.5 Switching Characteristics                      |     |

| 18.5.1 Clocks                                       |     |

| 18.5.2 Reset                                        |     |

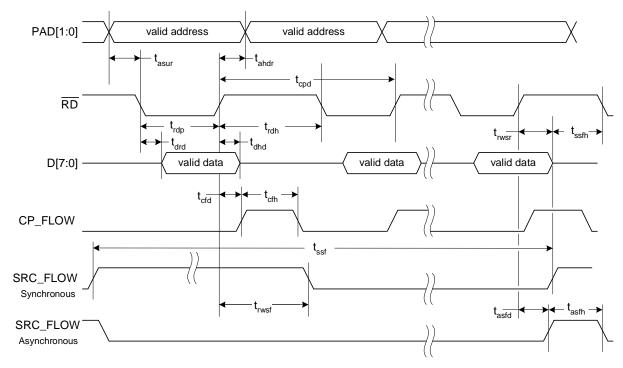

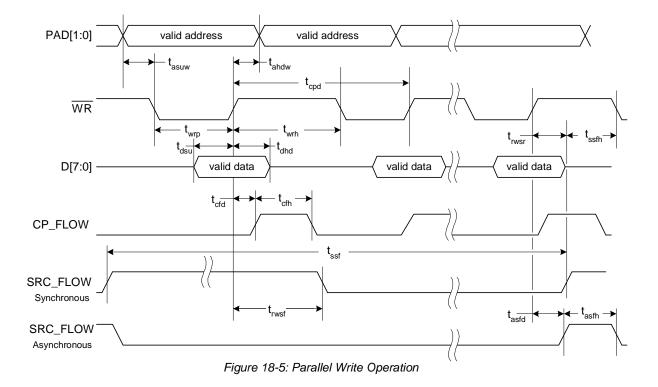

| 18.5.3 Parallel Interface                           |     |

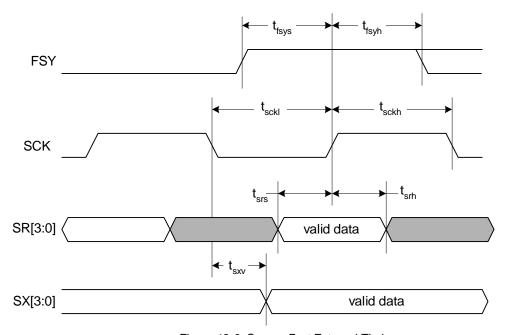

| 18.5.4 Source Ports (Serial) External Clocking      |     |

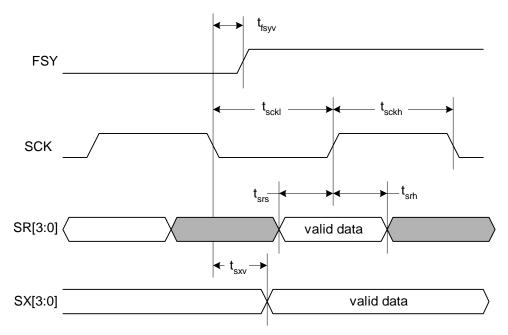

| 18.5.5 Source Ports (Serial) Internal Clocking      |     |

| 18.5.7 Control Port in I <sup>2</sup> C Mode        |     |

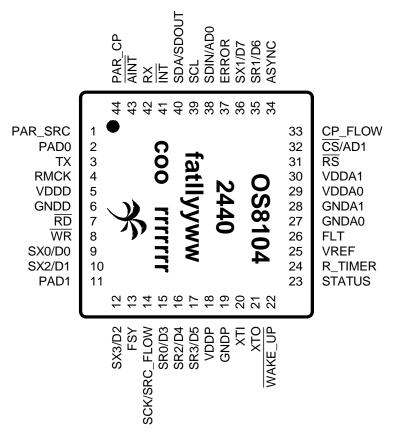

| 19 PACKAGING AND PINOUT                             |     |

|                                                     |     |

| 19.1 Pinout List                                    |     |

| 19.2 Low-Power/Zero-Power Mode Pin State            |     |

| 19.3 Reset Pin State                                |     |

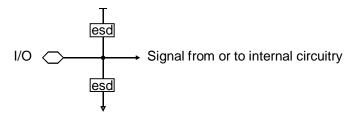

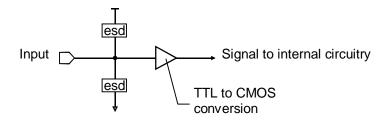

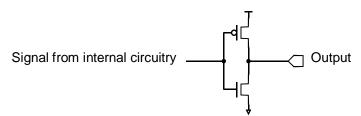

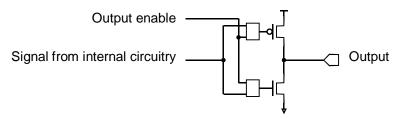

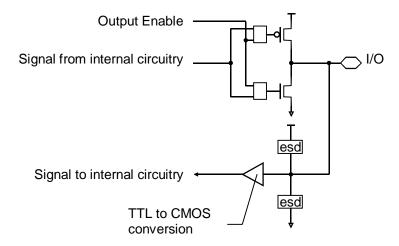

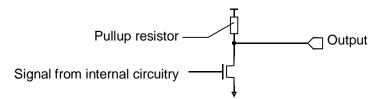

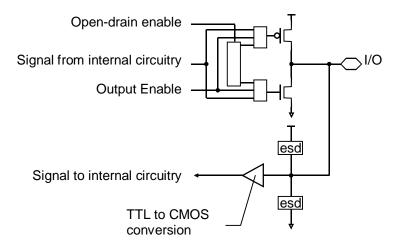

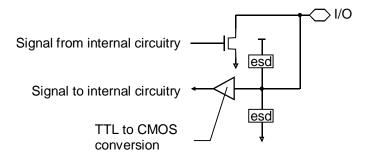

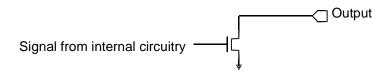

| 19.4 Equivalent Schematics For Pins                 |     |

| 19.6 Pinout                                         |     |

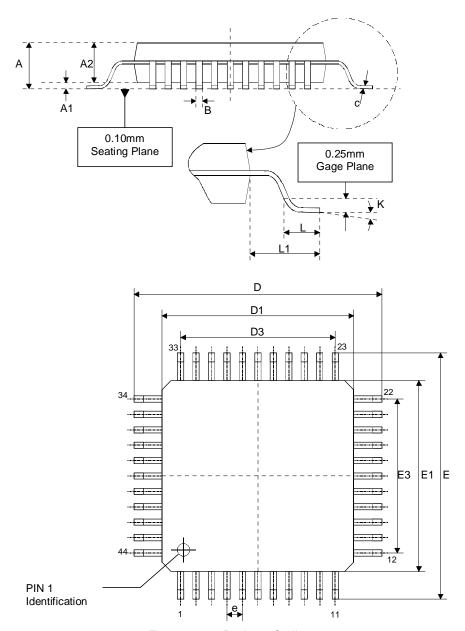

| 19.7 Package Outline (TQFP 44)                      |     |

| 20 APPLICATION INFORMATION                          |     |

| 20.1 Crystal Oscillator Selection                   | _   |

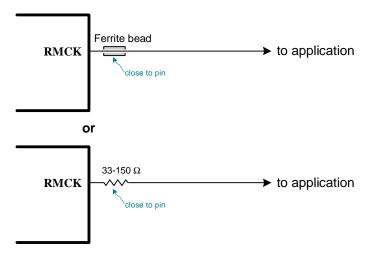

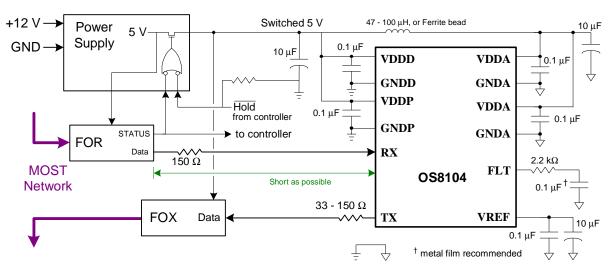

| 20.2 Power Supplies and Analog Components           |     |

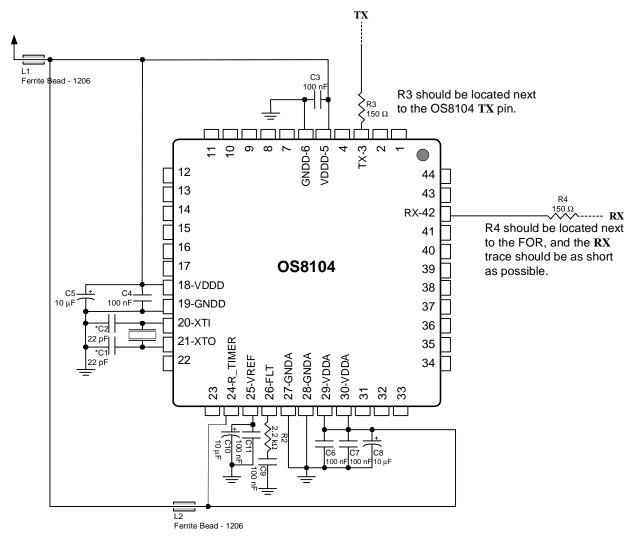

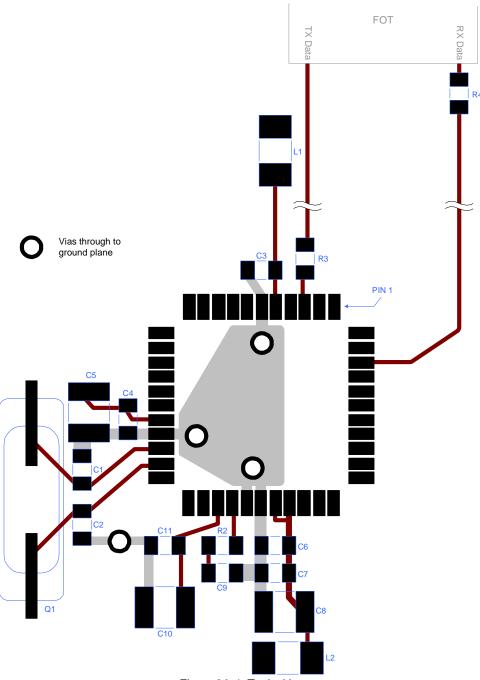

| 20.3 Layout Guidelines                              |     |

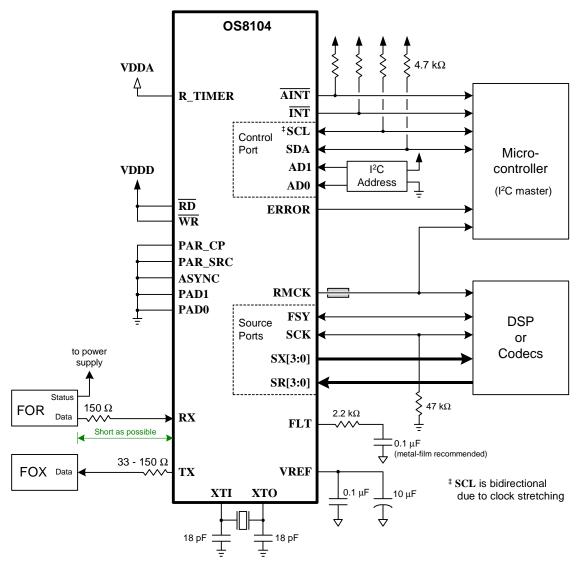

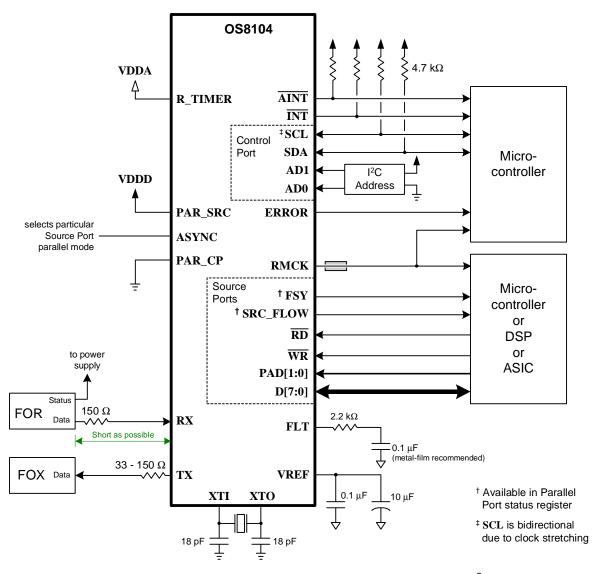

| 20.4 Control Port in I <sup>2</sup> C Serial Mode   |     |

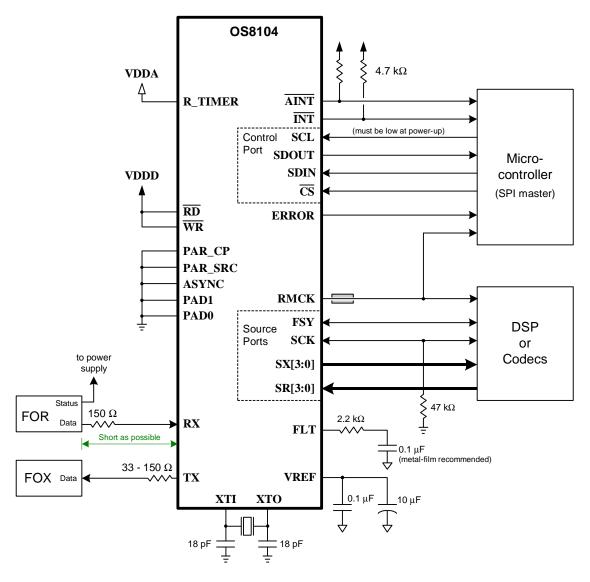

| 20.5 Control Port in SPI Serial Mode                |     |

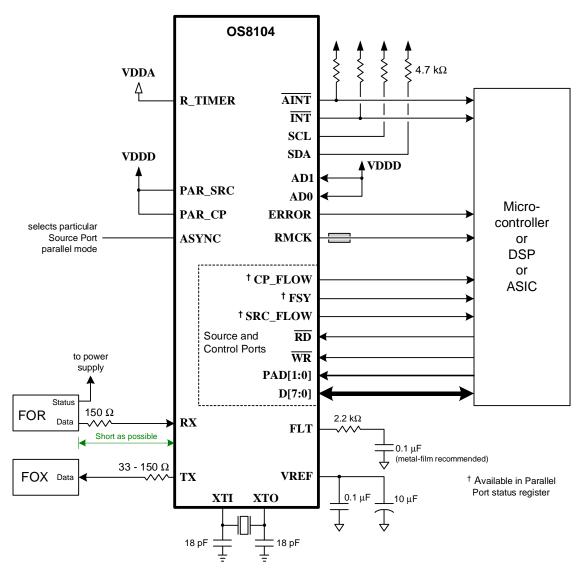

| 20.6 Parallel Source Ports, I2C Serial Control Port |     |

| 20.7 Source Ports and Control Port in Parallel      |     |

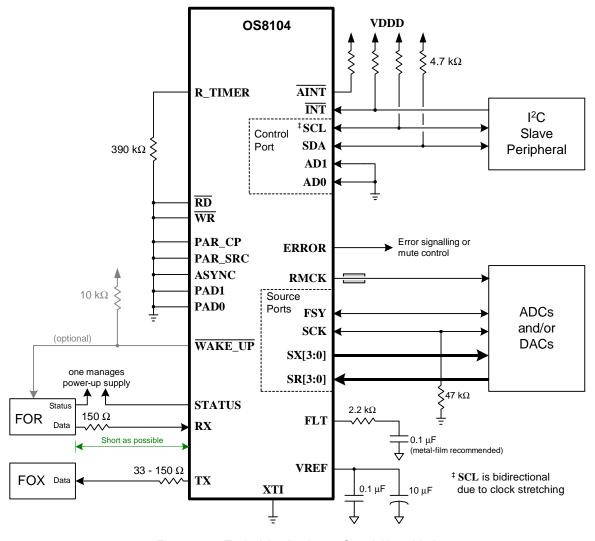

| 20.8 Stand-Alone Mode                               |     |

| APPENDIX A: REFERENCES                              | 189 |

| APPENDIX B: REGISTER OVERVIEW                       | 191 |

| APPENDIX C: DATA SHEET REVISION HISTORY             | 193 |

| INDEV                                               | 405 |

## **LIST OF FIGURES**

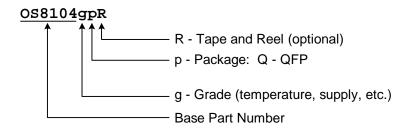

| Figure 1-1:  | Typical MOST Hardware/Software System Overview                   | 16       |

|--------------|------------------------------------------------------------------|----------|

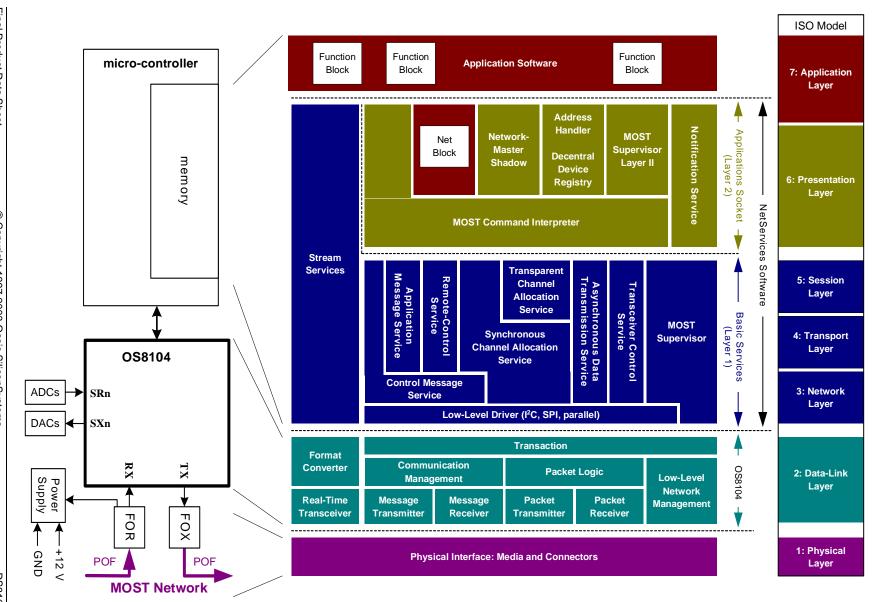

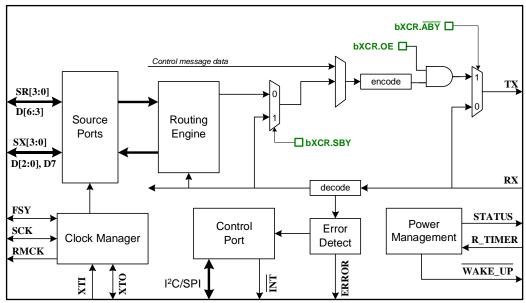

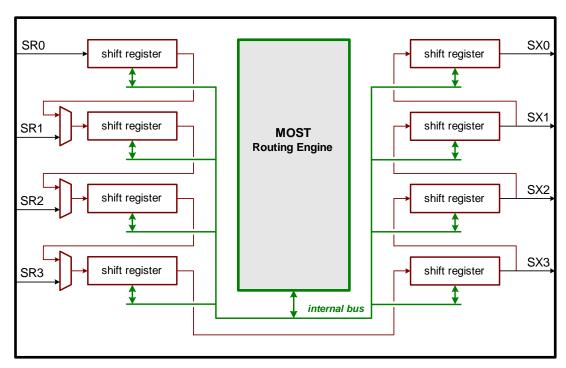

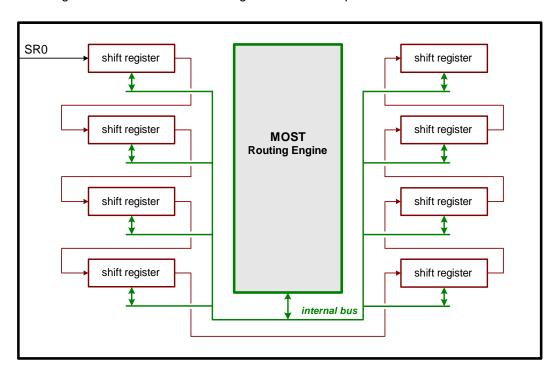

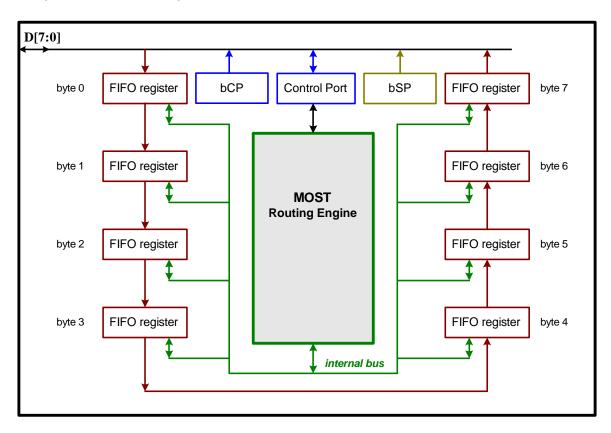

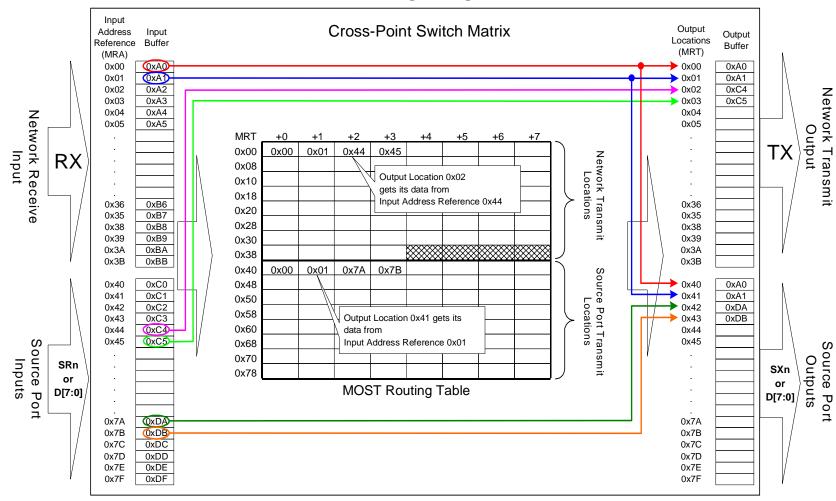

| Figure 2-1:  | MOST Routing Engine                                              |          |

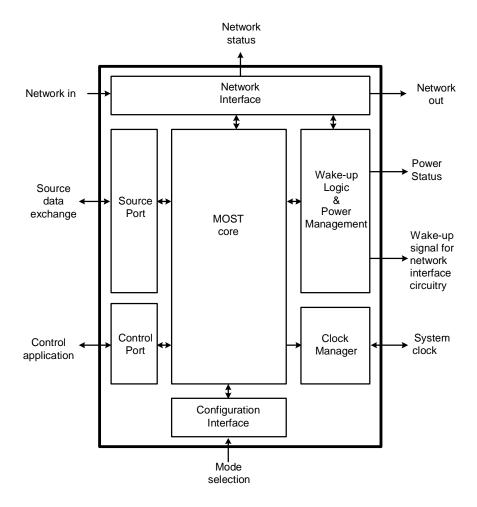

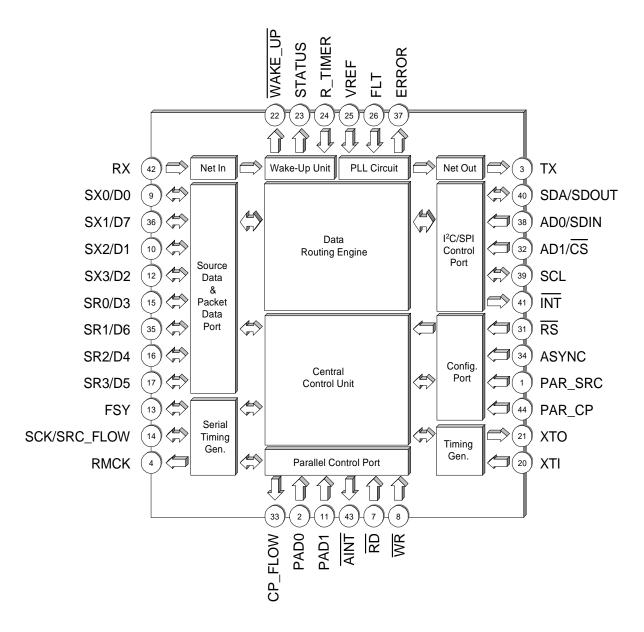

| Figure 3-1:  | OS8104 Functional Blocks                                         |          |

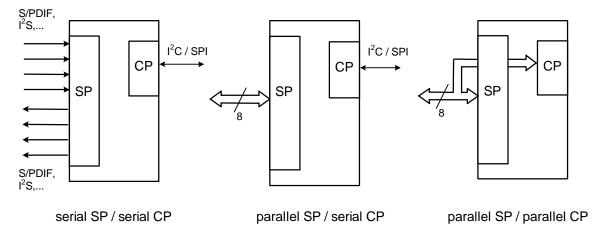

| Figure 4-1:  | Source and Control Port Interface Options                        |          |

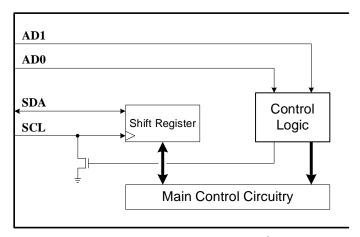

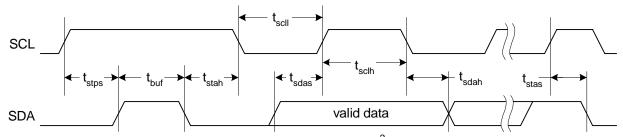

| Figure 5-1:  | Control Port Block Diagram (I <sup>2</sup> C Mode)               | 30       |

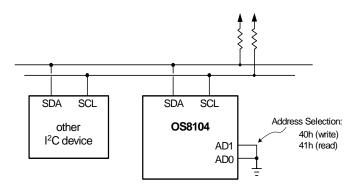

| Figure 5-2:  | Control Port Pin Connections (I <sup>2</sup> C Mode)             | 30       |

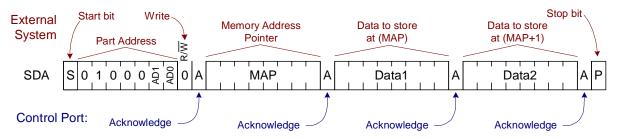

| Figure 5-3:  | Control Port Write Sequence (I <sup>2</sup> C Mode)              | 31       |

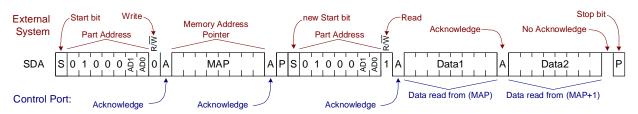

| Figure 5-4:  | Control Port Read Sequence (I <sup>2</sup> C Mode)               | 32       |

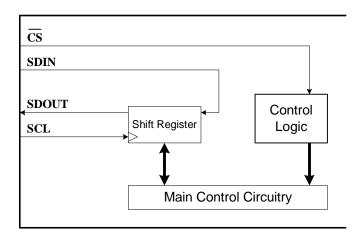

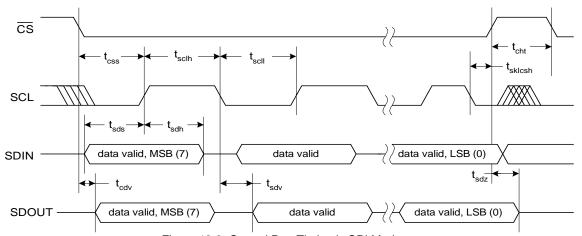

| Figure 5-5:  | Control Port Block Diagram (SPI Mode)                            | 33       |

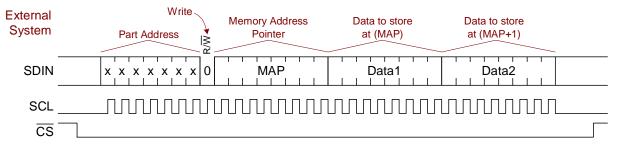

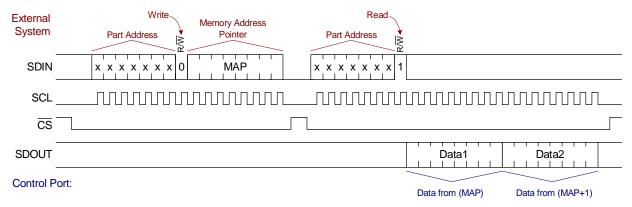

| Figure 5-6:  | Control Port Write Sequence (SPI Mode)                           | 33       |

| Figure 5-7:  | Control Port Read Sequence (SPI Mode)                            | 34       |

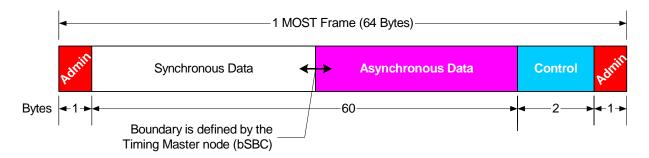

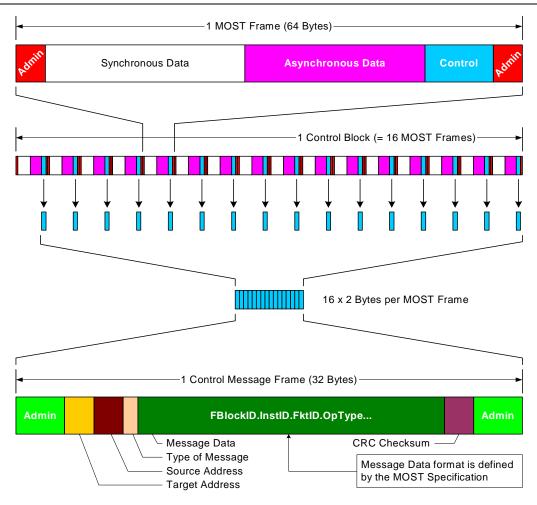

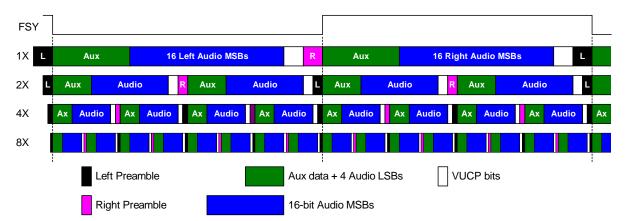

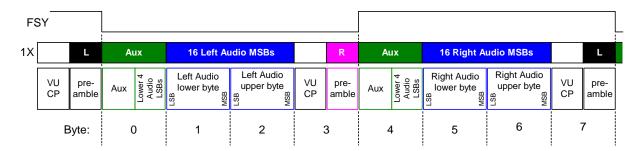

| Figure 6-1:  | General MOST Frame Structure                                     |          |

| Figure 6-2:  | Control Message Frame                                            | 36       |

| Figure 6-3:  | Network Interface Overview                                       |          |

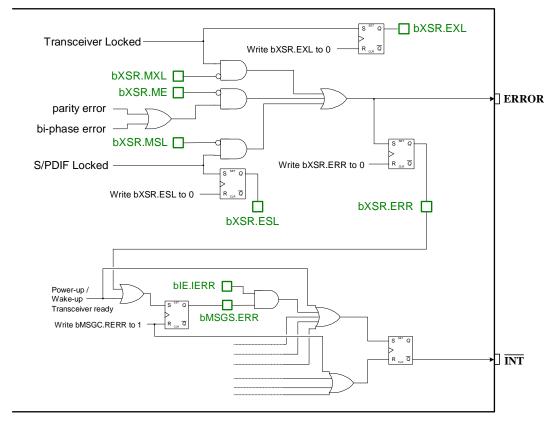

| Figure 6-4:  | Error Flags and Error Masks                                      | 39       |

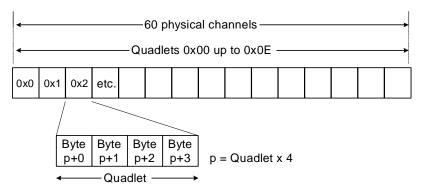

| Figure 6-5:  | Source Data Quadlets                                             |          |

| Figure 7-1:  | Source Port Block Diagram (Serial Mode)                          | 44       |

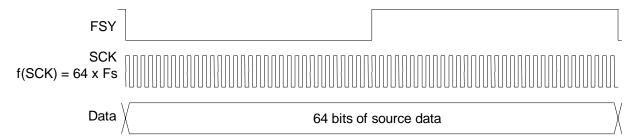

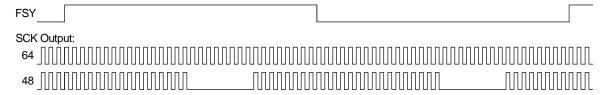

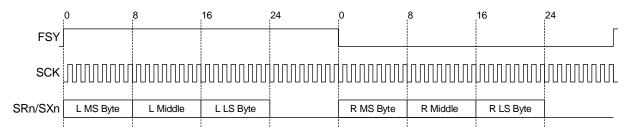

| Figure 7-2:  | Source Port at 64Fs                                              |          |

| Figure 7-3:  | Source Port Cascaded (Serial 512Fs Mode)                         |          |

| Figure 7-4:  | Source Port SCK Output Timing (bSDC1.EDG = 0)                    |          |

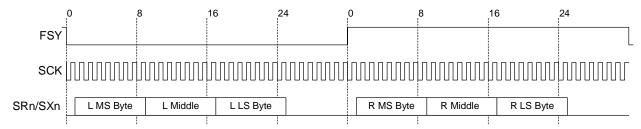

| Figure 7-5:  | I <sup>2</sup> S Source Data Format                              |          |

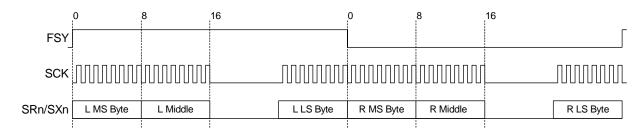

| Figure 7-6:  | Sony Source Data Format                                          |          |

| Figure 7-7:  | Matsushita Source Data Format                                    |          |

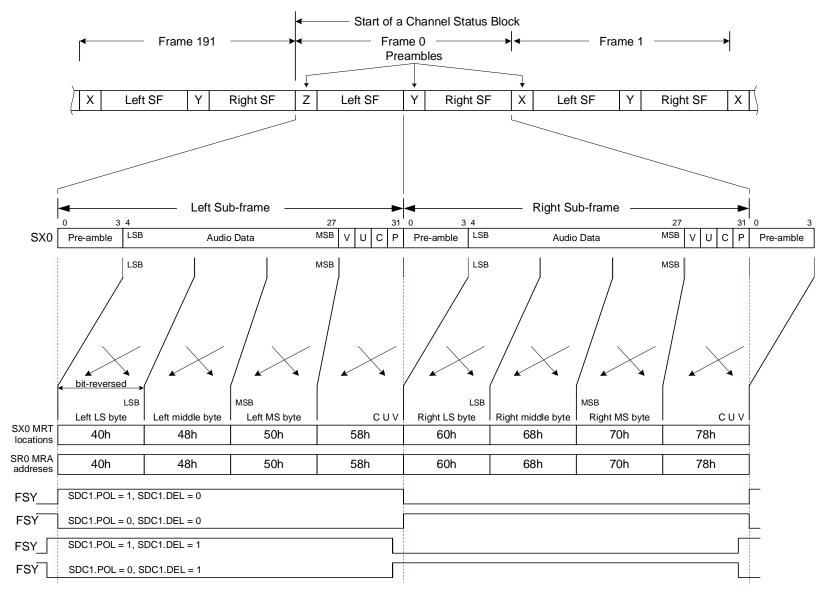

|              | Standard S/PDIF Data Stream                                      |          |

|              | SPS Bit Block Diagram                                            |          |

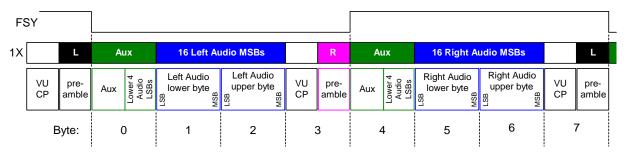

| Figure 7-10: | Source Port S/PDIF Format MRT/MRA                                | 57       |

|              | FSY – S/PDIF Alignment                                           |          |

|              | S/PDIF Byte Sequence                                             |          |

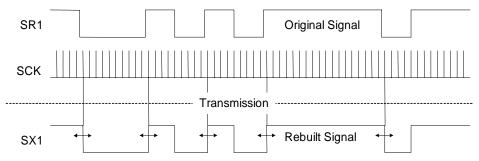

|              | Transparent Signal Transmission                                  |          |

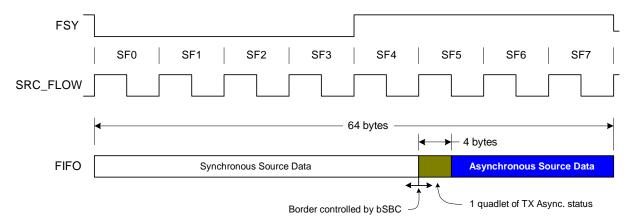

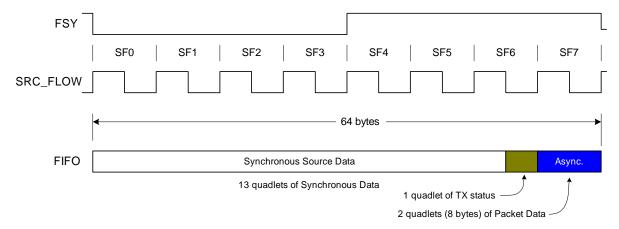

|              | Source Ports (FIFO) in Parallel Mode                             |          |

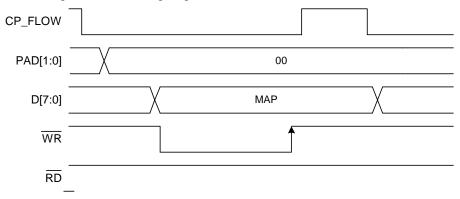

|              | Control Port MAP Data Register Write Timing (Parallel Mode)      |          |

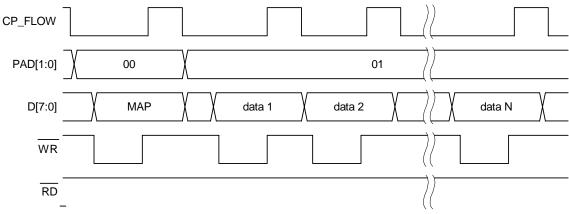

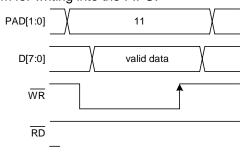

| Figure 8-3:  | Control Port Write Timing (Parallel Mode)                        |          |

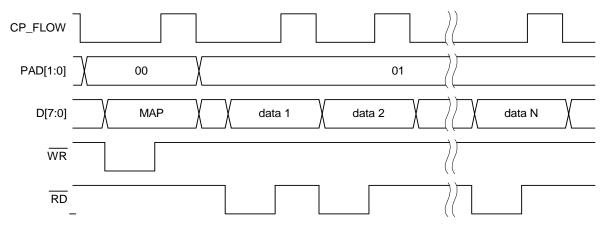

| Figure 8-4:  | Control Port Read Timing (Parallel Mode)                         |          |

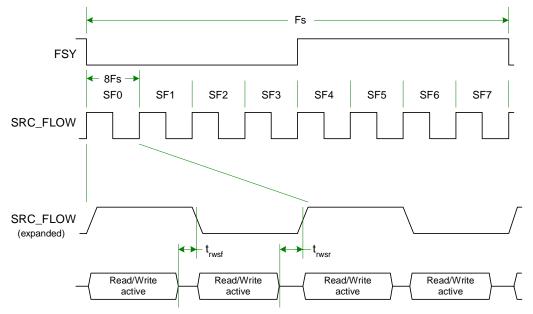

| Figure 8-5:  | Source Port Parallel-Synchronous Mode Timing Overview            |          |

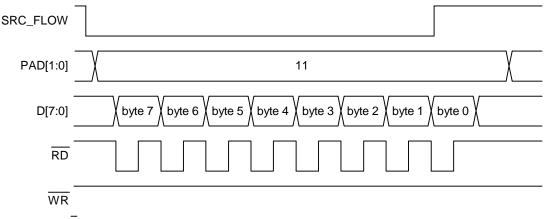

| Figure 8-6:  | Source Port Read Timing (Parallel-Synchronous Mode)              |          |

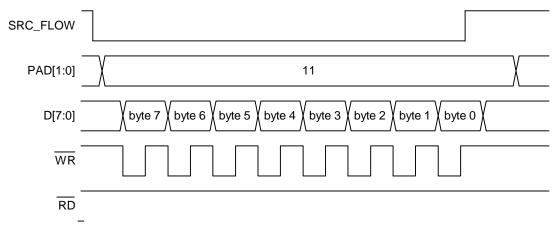

| Figure 8-7:  | Source Port Write Timing (Parallel-Synchronous Mode)             |          |

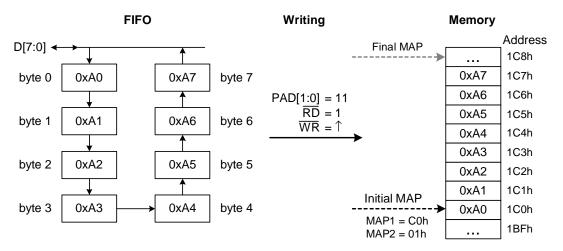

| Figure 8-8:  | Source Port Parallel-Asynchronous Mode Write Timing Overview     |          |

| Figure 8-9:  |                                                                  |          |

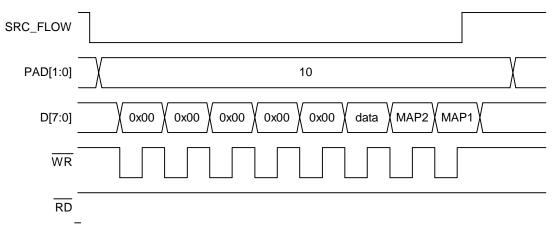

|              | Source Port Writing MAP Timing (Parallel-Asynchronous Mode)      |          |

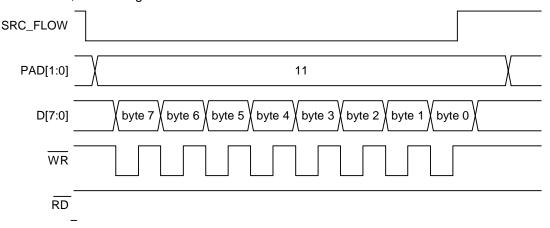

| Figure 8-11: | Source Port Writing 8 Bytes Timing (Parallel-Asynchronous Mode)  | 70<br>71 |

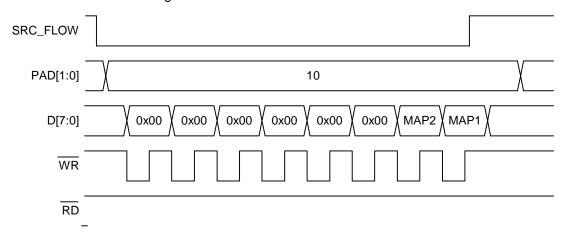

|              | Source Port Writing One Byte Timing (Parallel-Asynchronous Mode) |          |

|              | Source Port Reading 8 Bytes Timing (Parallel-Asynchronous Mode)  |          |

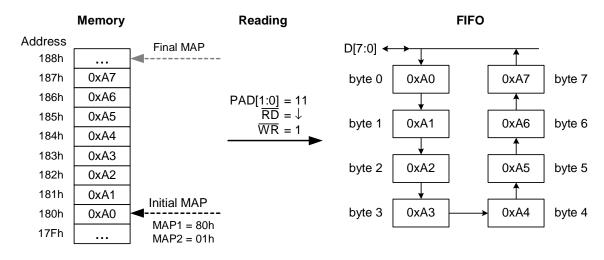

|              | Source Port Parallel-Asynchronous Read Data Mapping Example      |          |

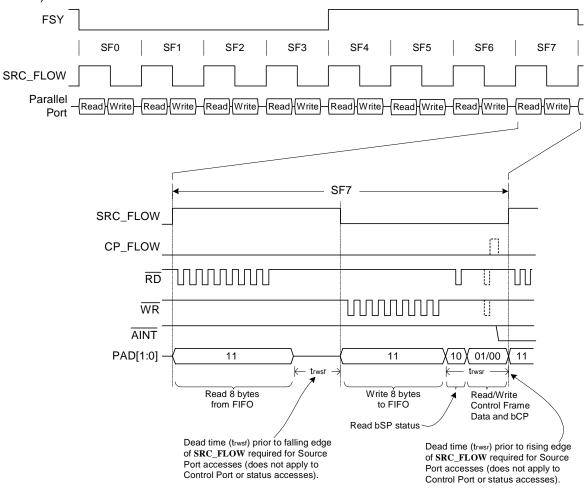

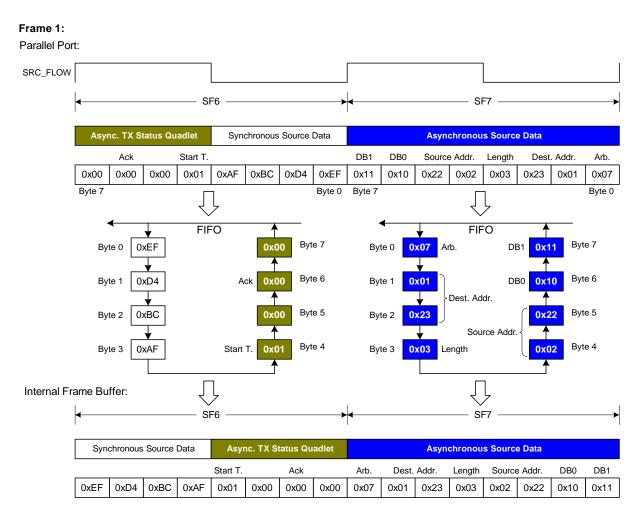

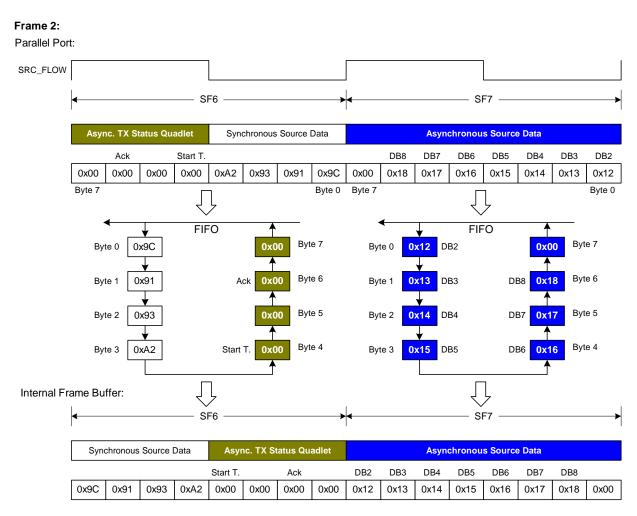

|              | Parallel-Combined Mode Timing                                    |          |

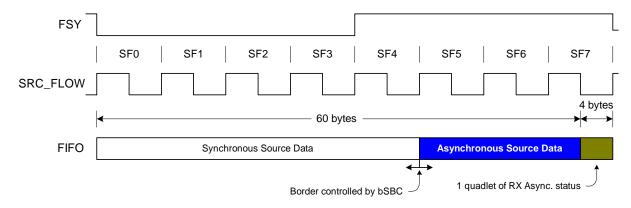

| Figure 8-16: | Parallel-Combined Mode Data Output (Network Received Data)       | 77<br>77 |

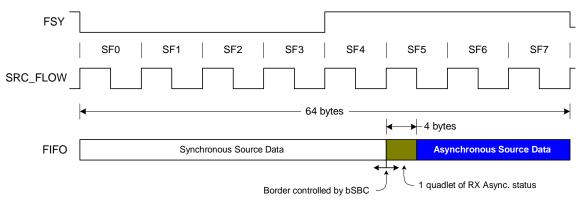

|              | Parallel Port Data Output (Network Received Data) — Moved Status |          |

|              | Program Flow for Receiving Packet Data (Parallel-Combined Mode)  |          |

|              | Parallel Port Data Input (Network Transmit Data)                 |          |

| Figure 0-19. | Packet Example — Source Data Allocation                          | ດາ<br>ດາ |

|              |                                                                  |          |

|              | Asynchronous Packet Example — Frame 1                            |          |

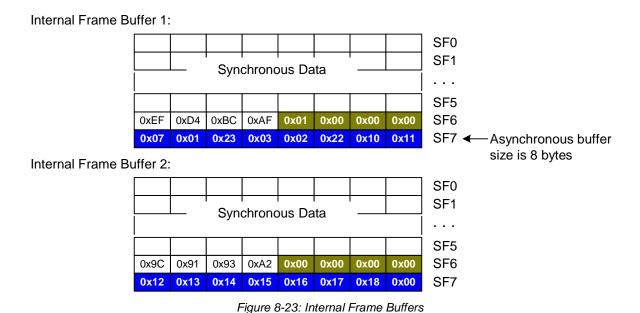

|              | Internal Frame Buffers                                           |          |

|              |                                                                  |          |

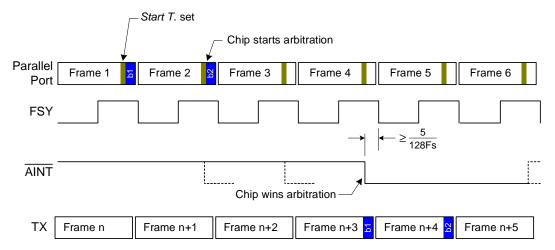

|              | Asynchronous Packet Example Arbitration                          |          |

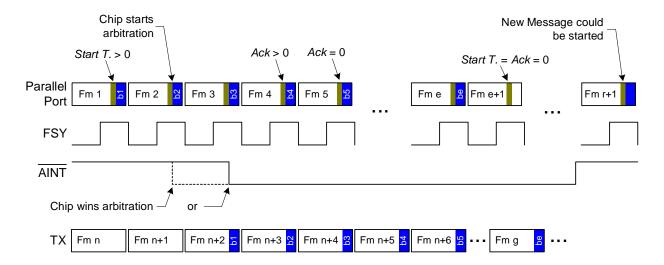

|              | Packet Buffering with No Delay                                   |          |

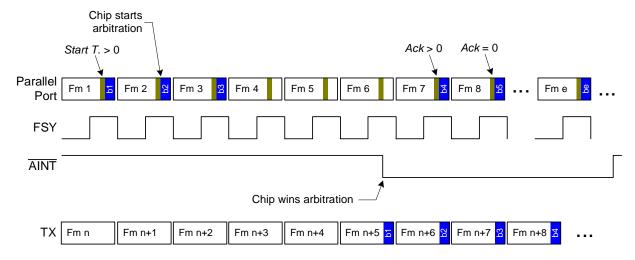

|              | Packet Buffering with Delay                                      |          |

| rigure 9-1:  | Clock Manager                                                    | 89       |

## O-A-S-I-S SiliconSystems

| Figure 9-2: Standard Application for VREF and FLT Pins                                                |     |

|-------------------------------------------------------------------------------------------------------|-----|

| Figure 9-3: Crystal Oscillator Input                                                                  |     |

| Figure 11-1: Multiple-Interrupt Events                                                                |     |

| Figure 12-1: Routing Engine                                                                           |     |

| Figure 12-2: Routing Process Example                                                                  | 99  |

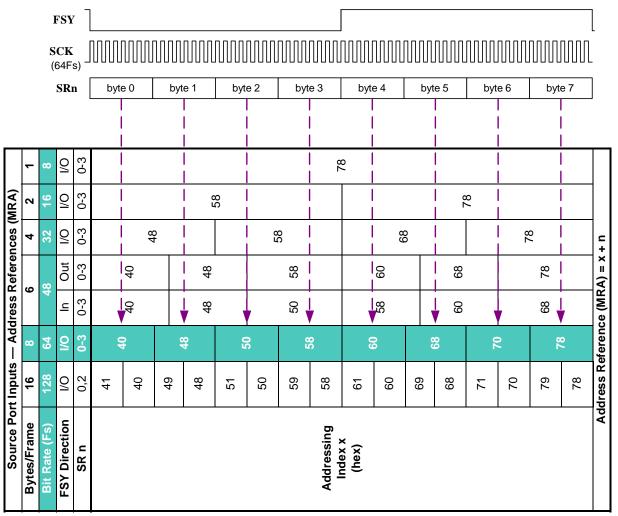

| Figure 12-3: Source Port Serial Format: Table vs. SRn Example                                         |     |

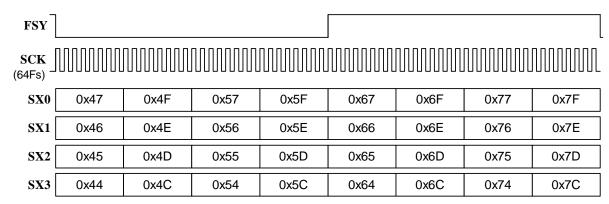

| Figure 12-4: Source Port Output Routing Example (MRT Locations)                                       |     |

| Figure 12-5: MRT Power-up Defaults                                                                    |     |

| Figure 13-1: Control Message Types                                                                    | 111 |

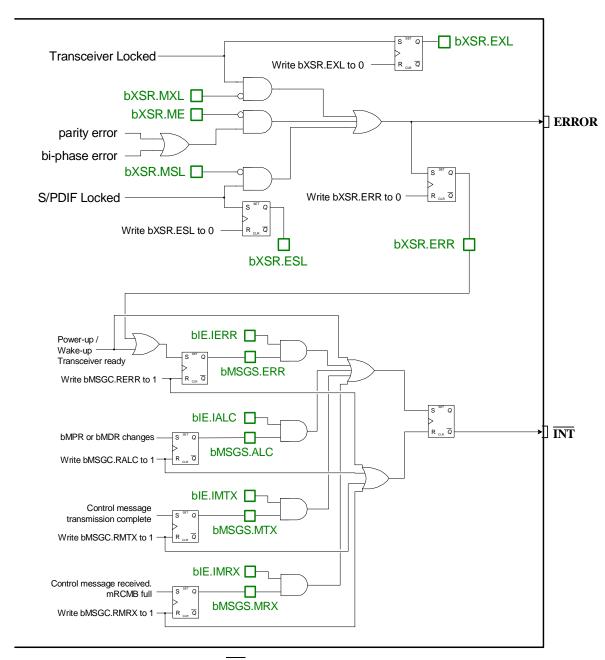

| Figure 13-2: INT and ERROR Pins Logical Schematic                                                     |     |

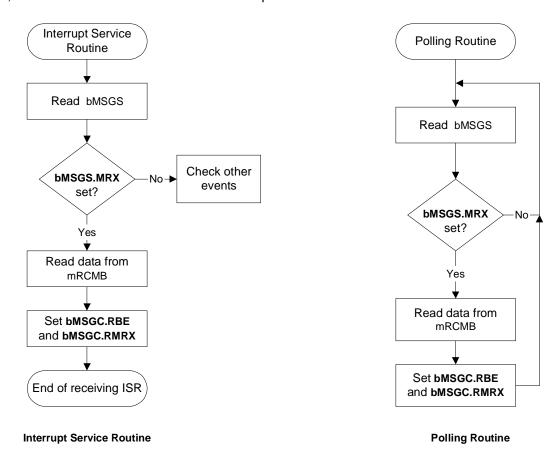

| Figure 13-3: Control Message Reception Flow                                                           | 121 |

| Figure 13-4: Sending MOST Control Messages: Interrupt Service Routine                                 |     |

| Figure 13-5: Sending MOST Control Messages: Polling                                                   |     |

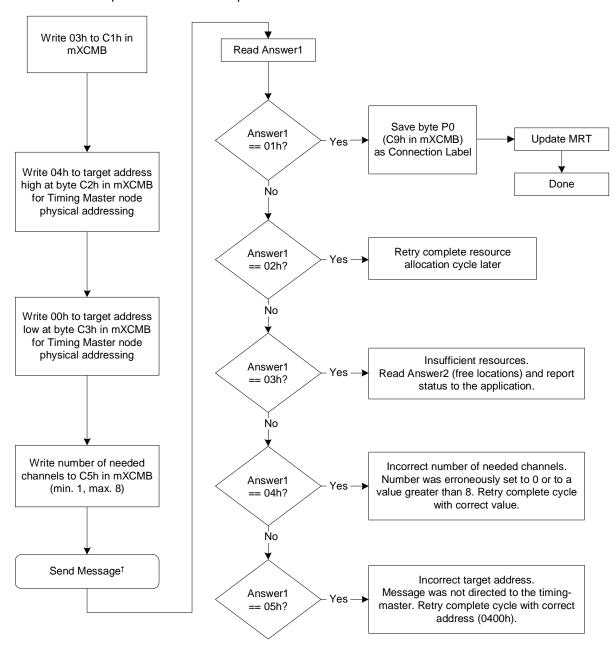

| Figure 13-6: Resource Allocation Flow                                                                 | 128 |

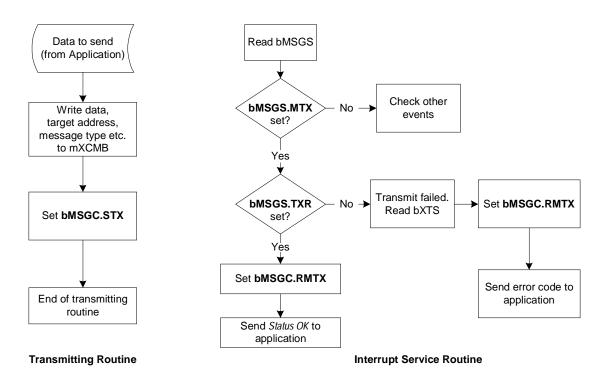

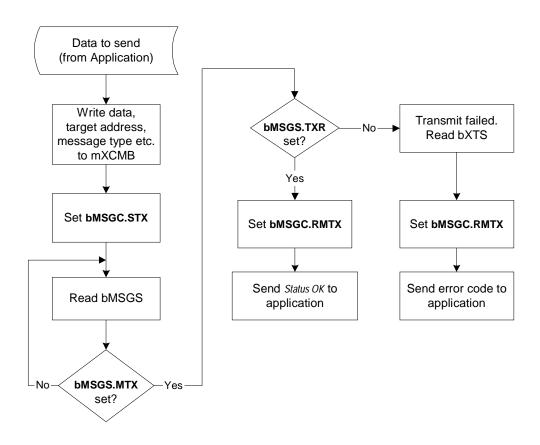

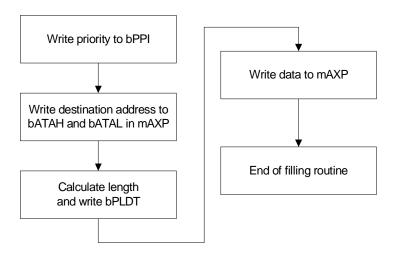

| Figure 15-1: Preparing Packet Data for Transmission                                                   |     |

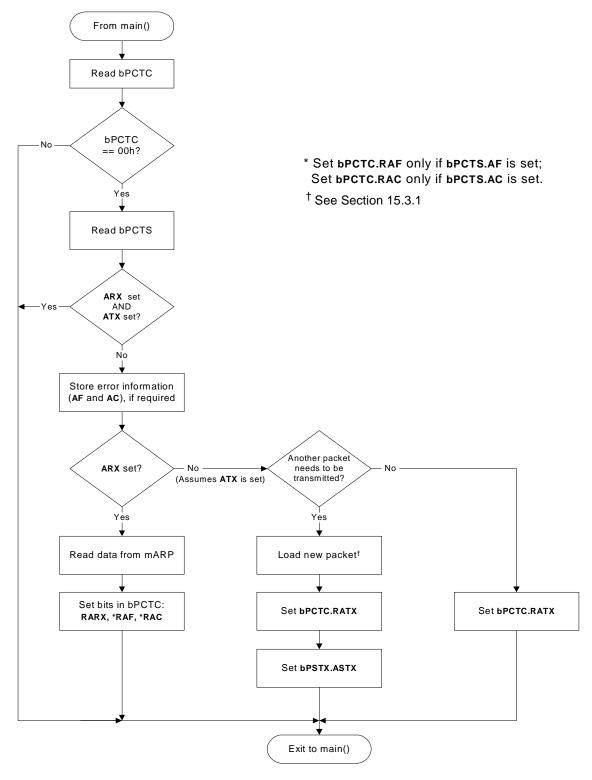

| Figure 15-2: Handling Packet Data Transfer by Polling                                                 |     |

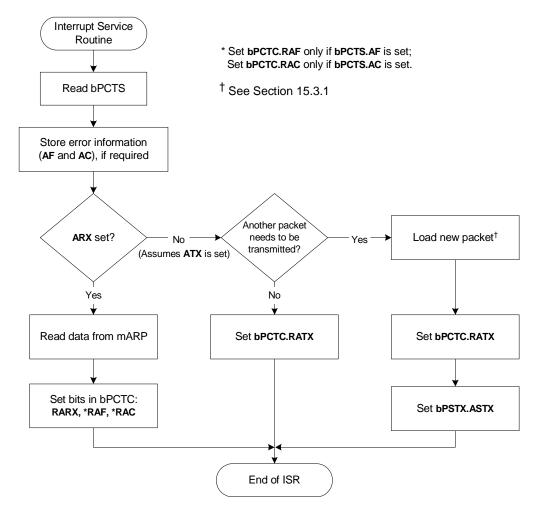

| Figure 15-3: Handling Packet Data Transfer via Interrupt                                              |     |

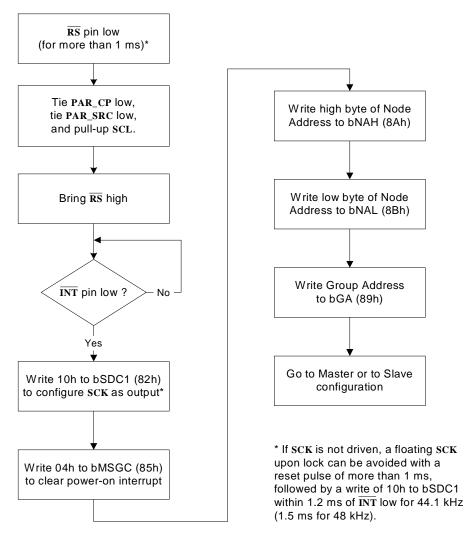

| Figure 16-1: Starting up - Initial Flow                                                               |     |

| Figure 16-2: Starting up - Timing-Master Configuration                                                |     |

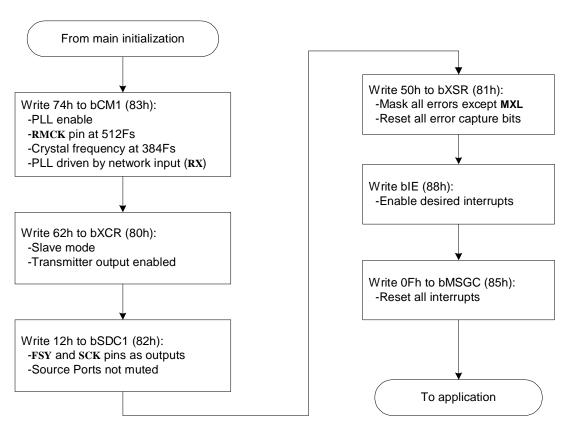

| Figure 16-3: Starting up - Timing-Slave Configuration                                                 | 146 |

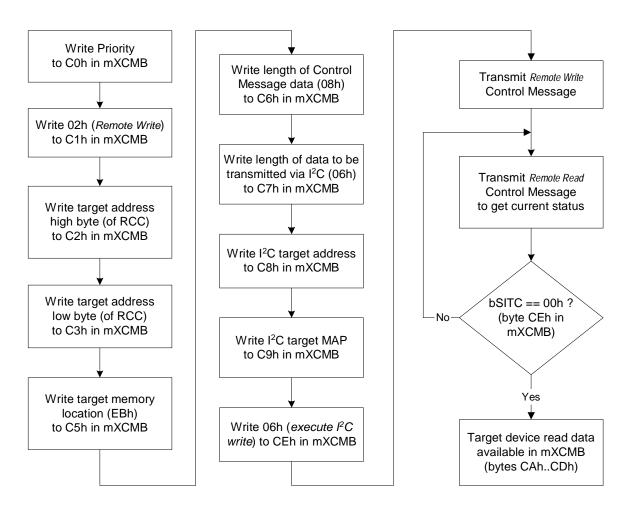

| Figure 17-1: Stand-Alone Mode: Write Flow                                                             |     |

| Figure 17-2: Stand-Alone Mode: Read Flow                                                              |     |

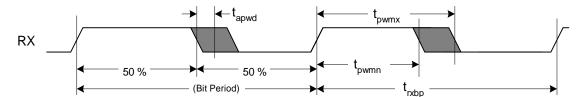

| Figure 18-1: RX Pulse-Width Distortion                                                                |     |

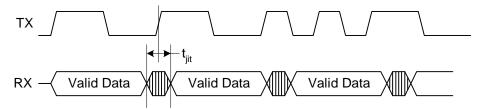

| Figure 18-2: RX Jitter                                                                                |     |

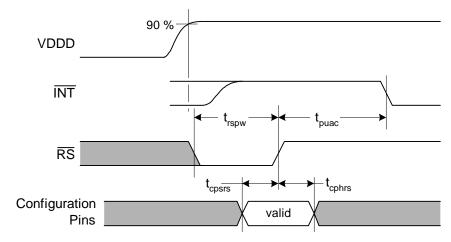

| Figure 18-3: Reset Pulse Width                                                                        |     |

| Figure 18-4: Parallel Read Operation                                                                  |     |

| Figure 18-5: Parallel Write Operation                                                                 |     |

| Figure 18-6: Source Port External Timing                                                              |     |

| Figure 18-7: Source Port Internal Timing                                                              | 163 |